信号滤波器

时间: 2024-12-16 00:27:49 | 作者: 信号滤波器

构建具有纳伏级灵敏度的电压测量系统会遇到很多设计挑战,目前较好的运算放大器(比如AD797)能轻松实现低于1nV/ Hz的噪声性能(1 kHz),但低频率噪声限制了能轻松实现的噪声性能为大约50 nV p-p(0.1 Hz至10 Hz频段内)。过采样和平均能够更好的降低宽带噪声的rms贡献,但代价是牺牲了更高的数据速率,且功耗较高,但过采样不会降频谱密度,同时它对1/f区内的噪声无影响。此外,为避免来自后级的噪声贡献,就需要采用较大的前端增益,以此来降低了系统带宽。假如没有隔离,那么所有的接地反弹或干扰都一定会出现在输出端,并有可能破坏放大器及其输入信号的低内部噪声的局面。表现良好的可以简化设计,并降低共模电压、电源波动和温度漂移引起的残留误差。

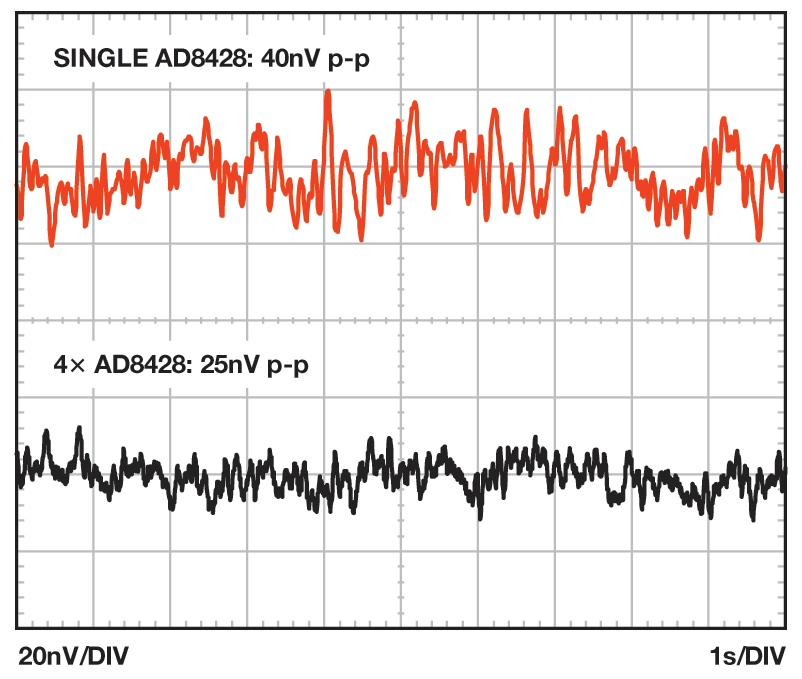

低噪声仪表放大器AD8428提供2000 精确增益,具备解决这样一些问题所必须的一切特性。AD8428 具有5 ppm/°C最大增益漂移、0.3 μV/°C最大失调电压漂移、140 dB最小CMRR至60 Hz(120 dB最小值至50 kHz)、130 dB最小PSRR和3.5 MHz带宽,适合低电平测量系统。引人注目的是该器件的1.3 nV/ Hz电压噪声(1 kHz)和40 nV p-p噪声(0.1 Hz至10 Hz)性能,在极小信号下具有高信噪比。两个额外的引脚可让设计人员改变增益或增加滤波器来降低噪声带宽。这些滤波器引脚还提供了降低噪声的独特方法。

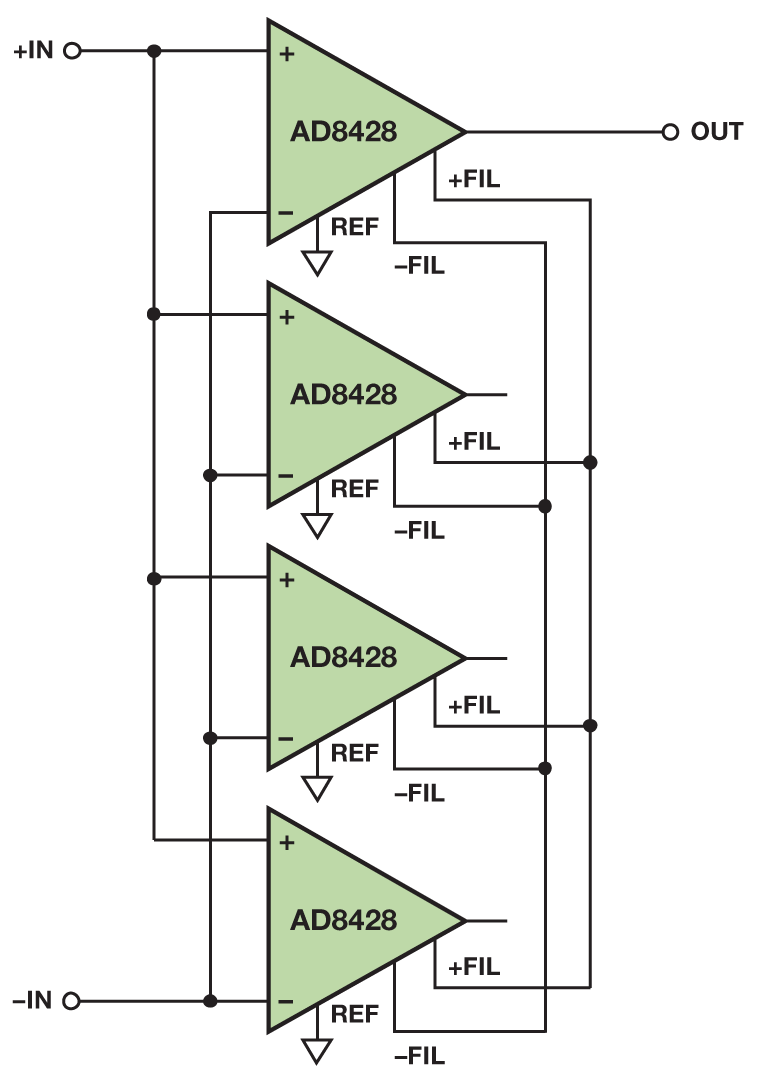

图1 显示的电路配置可逐步降低系统噪声。四个AD8428 的输入和滤波引脚互相短接,降低噪声至原来的二分之一。能够正常的使用任意一个仪表放大器的输出来保持低输出阻抗。此电路能扩展以此来降低噪声,降低的倍数为所用放大器数的平方根。

每一个AD8428 产生1.3 nV/ Hz折合到输入(RTI)的典型频谱噪声,该噪声与其他放大器产生的噪声不相关。不相关的噪声源以方和根(RSS)的方式叠加到滤波器引脚。另一方面,输入信号为正相关。每一个AD8428 都响应信号在滤波器引脚上生成相同的电压,因此连接多个AD8428 不会改变电压,增益保持为2000。

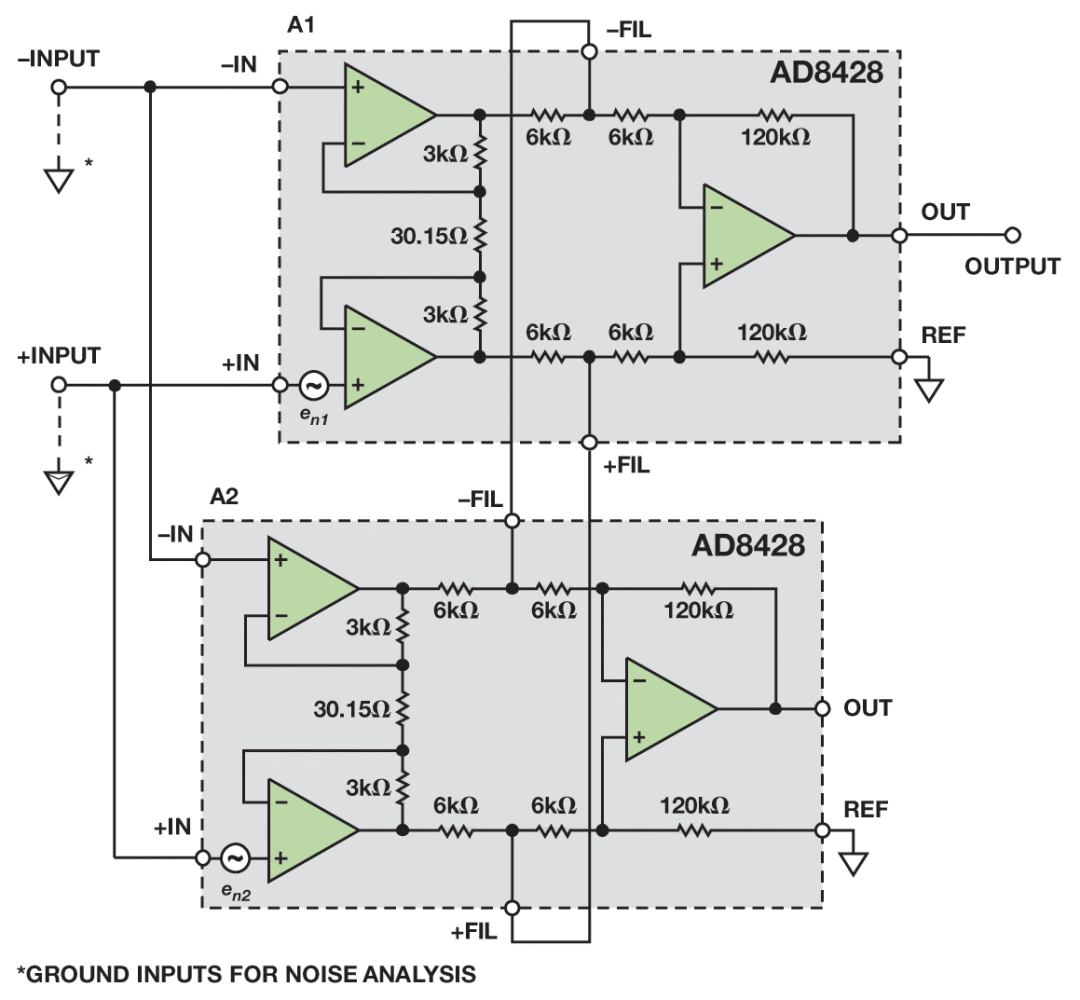

针对图2电路简化版本的分析表明,将两个AD8428以此方式连接能够更好的降低噪声,降低的倍数为2。每一个AD8428的噪声都可以在+IN引脚上建模。为了确定总噪声,可以将输入接地,并使用叠加来组合噪声源。

噪声源en1经200差分增益放大,并到达前置放大器A1的输出端。就这部分的分析而言,输入接地时,前置放大器A2的输出端无噪声。前置放大器A1每个输出端与相应前置放大器A2输出端之间的6 kΩ/6 kΩ电阻分频器能够使用戴维宁等效电路替代:前置放大器A1输出端噪声电压的一半以及一个3 kΩ串联电阻。这部分就是降低噪声的机制。完整的节点分析表明,响应en1的输出电压为1000 × en1。由于对称,因此响应噪声电压en2的输出电压为1000 × en2。en1和en2幅度都等于en,并且将作为RSS叠加,导致总输出噪声为1414 × en。

为了将其折合回输入端,就必须验证增益。假设在+INPUT和–INPUT之间施加差分信号VIN。A1第一级输出端的差分电压等于VIN × 200。同样的电压出现在前置放大器A2的输出端,因此没有分频信号进入6 kΩ/6 kΩ分频器,并且节点分析表明输出为VIN × 2000。因此,总电压噪声RTI为en× 1414/2000,等效于en/2。使用AD8428的1.3 nV/Hz典型噪声密度,则两个放大器配置所产生的噪声密度约为0.92 nV/Hz。

使用额外的放大器之后,滤波器引脚处的阻抗发生改变,逐步降低噪声。例如,如图1所示使用四个AD8428,则前置放大器输出端到滤波器引脚之间的6 kΩ电阻后接三个6 kΩ电阻,分别连接每一个无噪声前置放大器的输出端。这样便有效地创建了6 kΩ/2 kΩ电阻分频器,将噪声进行四分频处理。因此,正如预测的那样,四个放大器的总噪声便等于en/2。

主要的权衡取舍来自功耗与噪声。AD8428具有极高的噪声-功耗效率,输入噪声密度为1.3 nV/Hz(6.8 mA最大电源电流)。为了作对比,考虑低噪声AD797运算放大器——该器件需要10.5 mA最大电源电流来达到0.9 nV/Hz。一个分立式G = 2000低噪声仪表放大器采用两个AD797运算放大器和一个低功耗差动放大器构建,需要用21 mA以上电流,实现两个运算放大器和一个30.15 Ω电阻贡献的1.45 nV/Hz噪声RTI性能。

除了很多放大器并联连接使用的电源考虑因素外,设计人员还一定要考虑热环境。采用±5 V电源的单个AD8428因内部功耗会使温度上升约8°C。如果很多个器件靠近放置,或者放置在封闭空间,则它们之间会互相传导热量,需考虑使用热管理技术。04SPICE仿真

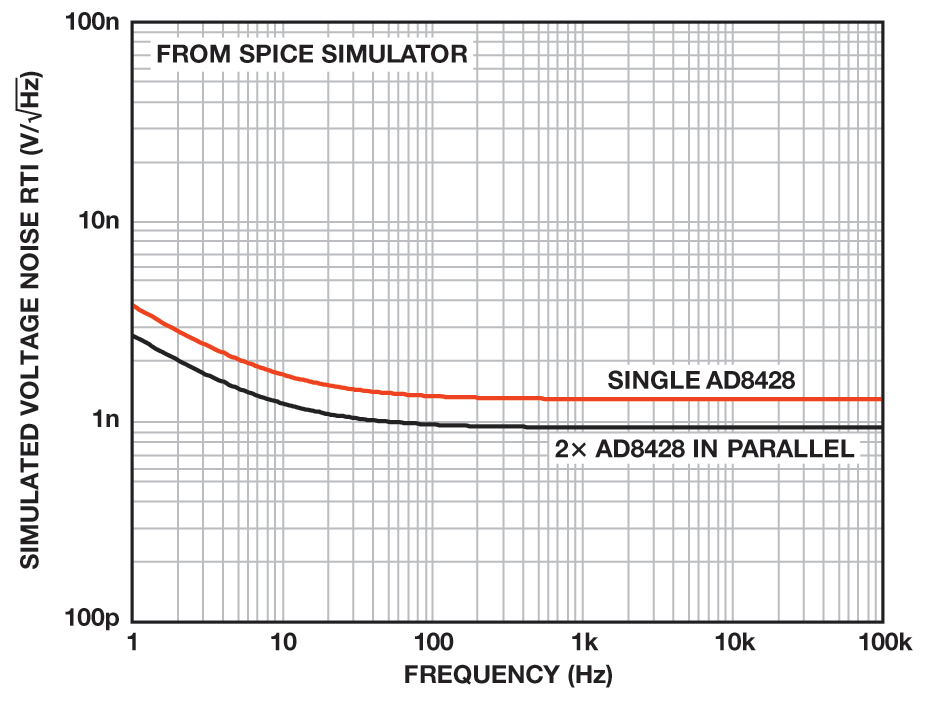

SPICE电路仿真虽然不能代替原型制作,但作为验证此类电路构想的第一步很有用。若要验证此电路,能够正常的使用ADIsimPE仿线 SPICE宏模型仿真两个器件并联时的电路性能。图3中的仿真根据结果得出该电路的表现与预期一致:增益为2000,噪声降低30%。

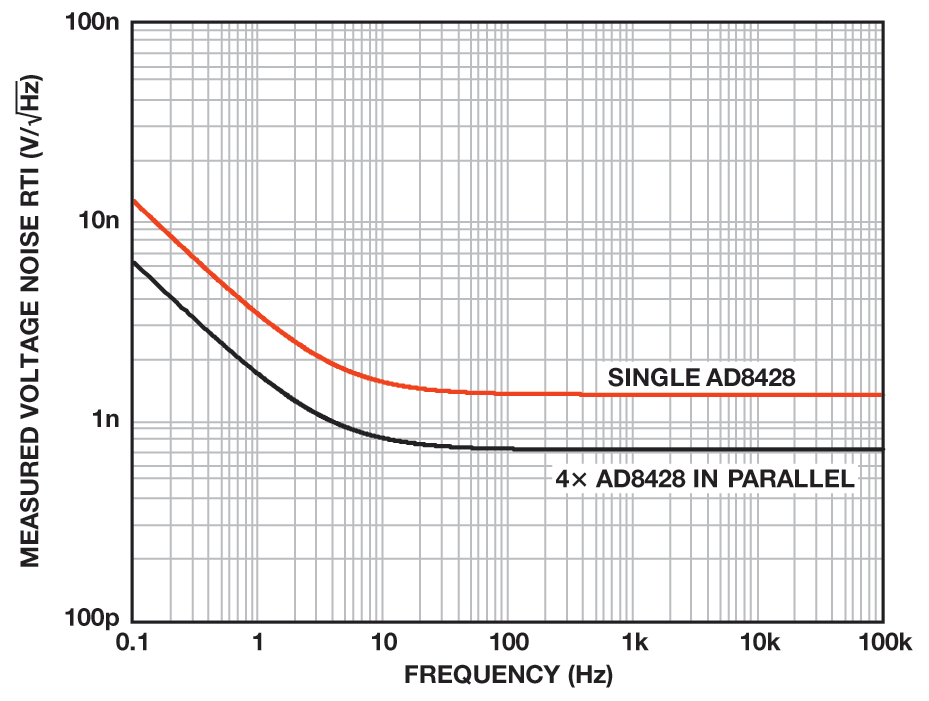

在工作台上测量四个AD8428组成的完整电路。测得的RTI噪声频谱密度为0.7 nV/Hz (1 kHz),0.1 Hz至10 Hz范围内具有25 nV p-p。这比很多纳伏电压表的噪声都要更低。测得的噪声频谱和峰峰值噪声分别如图4和图5所示。

纳伏级灵敏度目标非常难以达成,会遇到很多设计挑战。对需要低噪声和高增益的系统,AD8428仪表放大器具有实现高性能设计所需的特性。此外,该器件独特的配置允许将这个不寻常的电路加入其纳伏级工具箱内。